SRAM IP 使用规范

1. 尺寸

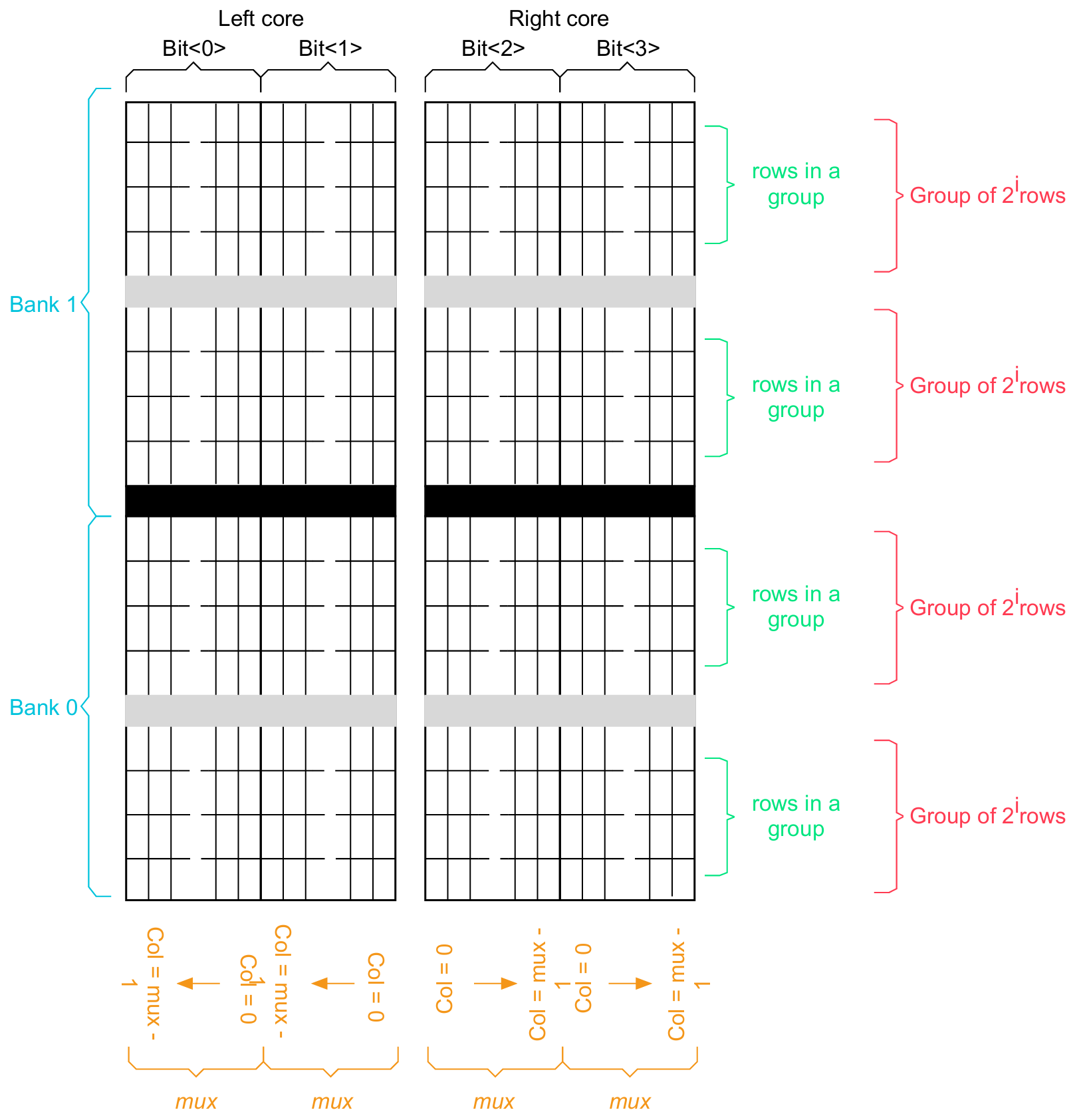

SRAM 的尺寸是由 Number of Words、Number of Bits、Multiplexer Width Number of banks 所决定的,对应能生成的 SRAM 尺寸如下表所示。

| Mux | Flexible_banking | Words (min:max:step) | Bits (min:max:step) |

|---|---|---|---|

| 4 | 2 | 512:2048:32 | 4:160:1 |

| 4 | 4 | 1024:4096:64 | 4:160:1 |

| 4 | 8 | 2048:8192:128 | 4:160:1 |

| 8 | 2 | 1024:4096:64 | 4:160:1 |

| 8 | 4 | 20048:8192:128 | 4:160:1 |

| 8 | 8 | 4096:16384:256 | 4:160:1 |

| 16 | 2 | 2048:8192:128 | 4:80:1 |

| 16 | 4 | 4096:16384:256 | 4:80:1 |

| 16 | 8 | 8192:32768:512 | 4:80:1 |

对于逻辑尺寸相同的 SRAM,Bank 的数量并不会显著影响面积。 Mux 越多,SRAM 的 Wordline 越长,Bitline 越短。

2. 端口

SRAM IP 的端口定义如下表所示。

| 端口 | 方向 | 描述 |

|---|---|---|

| VSSE | input | 接地 |

| VDDPE | input | I/O 以及外围电路供电 |

| VDDCE | input | SRAM 阵列供电 |

| CLK | input | 时钟 |

| A[m-1:0] | input | 地址 |

| D[n-1:0] | input | 写数据 |

| Q[n-1:0] | output | 读数据 |

| CEN | input | 片选,低电平有效 |

| WEN | input | 写使能,低电平有效 |

| RET1N | input | 保留模式,低电平有效 |

| EMA[2:0] | input | 裕量调整 |

| EMAW[1:0] | input | 写裕量调整 |

| EMAS | input | 灵敏放大器裕量调整 |

Bit Mask

如果加入了 Bit Mask 功能,则 WEN 信号会被替换为两个信号 GWEN,WEN[n-1:0]。

前者表示全局写使能(低电平有效),后者表示每个 Bit 的写使能(低电平有效)。

2.1 Extra Margin Adjustment (EMA)

EMA 允许 SRAM 添加内部时序延迟,以提高制造良率。 这些延迟减慢内存访问速度,为成功的内存读写操作提供了额外的时间。

EMA[2:0] 从 3'b000-3'b111 变化时,访问时间、周期时间和裕量分别增加。

即 3'b000 是最快设置,3'b111 最慢。

EMAW[1:0] 通过延长内部写脉冲来控制写操作的延迟。

随着 EMAW[1:0] 从 2'b00-2'b11 依次递增,裕量也依次增大。

最快的设置是 2'b00,最慢的设置是 2'b11。

EMAW[1:0] 的设置不会影响读操作期间的访问时间。

EMAS 扩展了检测放大器使能信号的脉冲宽度。

当驱动为高电平时,脉冲宽度会延长。

EMAS 不会影响访问时间。

EMA[2:0] 和 EMAW[1:0] 都会影响总周期时间。

Liberty 文件中的时间是读写时间的最坏情况。

EMA 配置

建议通过使用寄存器或复用外部引脚来控制 EMA 引脚。 如果 EMA 设置与默认设置不同,则必须能够在操作期间动态更改 EMA 设置。 不得将 EMA 引脚硬编码为默认值以外的任何值,否则后果自负!

2.2 Retention

保留模式允许降低 SRAM 供电电压。 这种低功耗模式会保留存储器阵列内容。 在此模式下无法进行读或写操作。

2.3 Vmin Assist (Read Assist)

读辅助添加了逻辑以改善位单元的读干扰裕度,确保读/写操作期间不会发生意外写入。

RAWL 配置

建议通过使用寄存器或复用外部引脚来控制 RAWL 引脚。 如果 RAWL 设置与默认设置不同,则必须能够在操作期间动态更改 RAWL 设置。 不得将 RAWL 引脚硬编码为默认值以外的任何值,否则后果自负!

2.4 Vmin Assist (Write Assist)

写入辅助添加了逻辑,以在低于典型值的电压下提高位单元的写入能力,从而确保写入操作期间的正确功能。

WABL 配置

建议通过使用寄存器或复用外部引脚来控制 WABL 引脚。 如果 WABL 设置与默认设置不同,则必须能够在操作期间动态更改 WABL 设置。 不得将 WABL 引脚硬编码为默认值以外的任何值,否则后果自负!

2.5 Self-time Overide (STOV)

STOV 功能允许覆盖存储器内部时钟脉冲的自定时生成。 该覆盖允许您使用非内部时钟脉冲进行芯片调试,因此可以在 SoC 中将该引脚实现为可编程。

STOV 配置

STOV 信号为高电平有效。 STOV 引脚仅用于测试目的,在正常操作期间不得置位,否则后果自负!

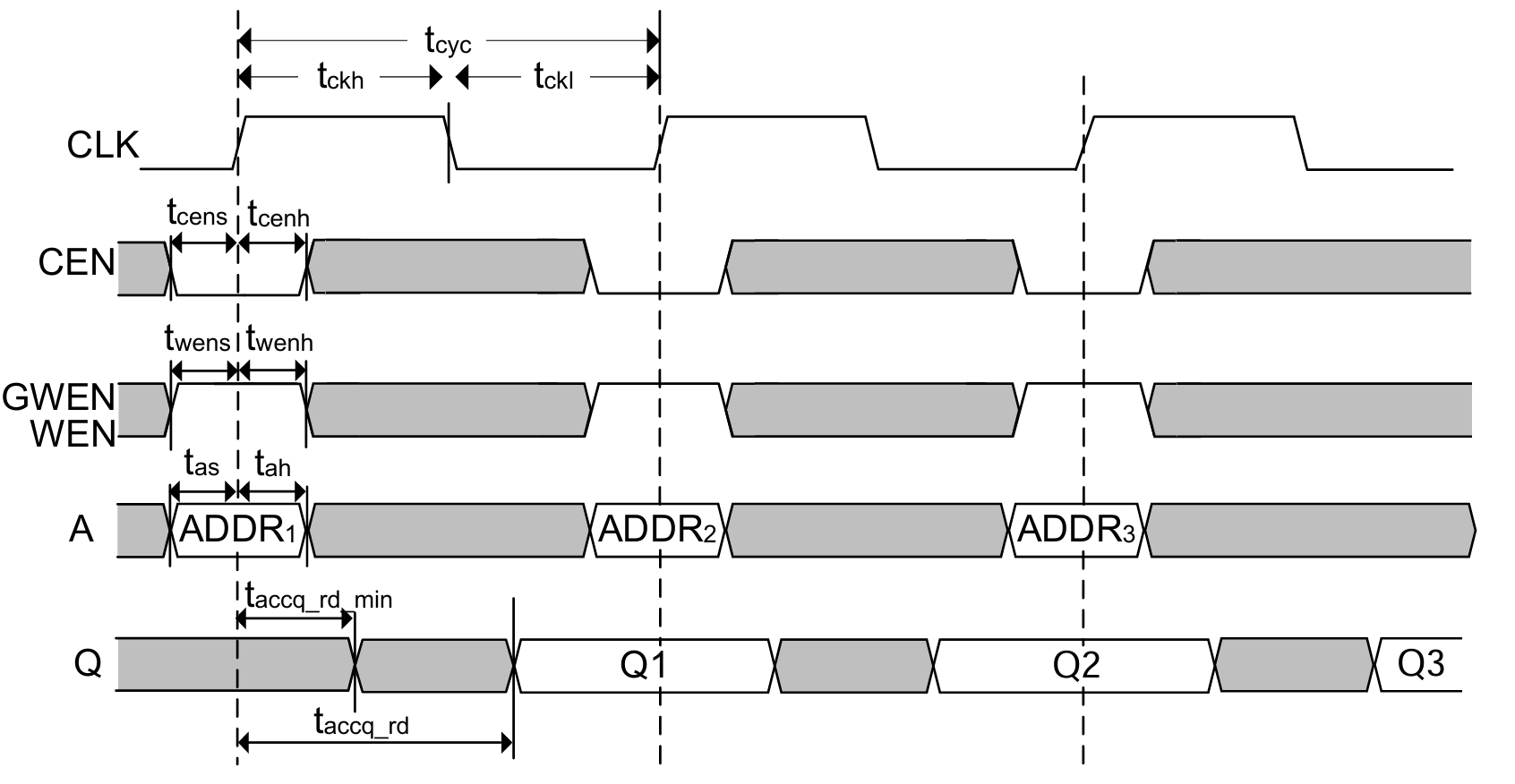

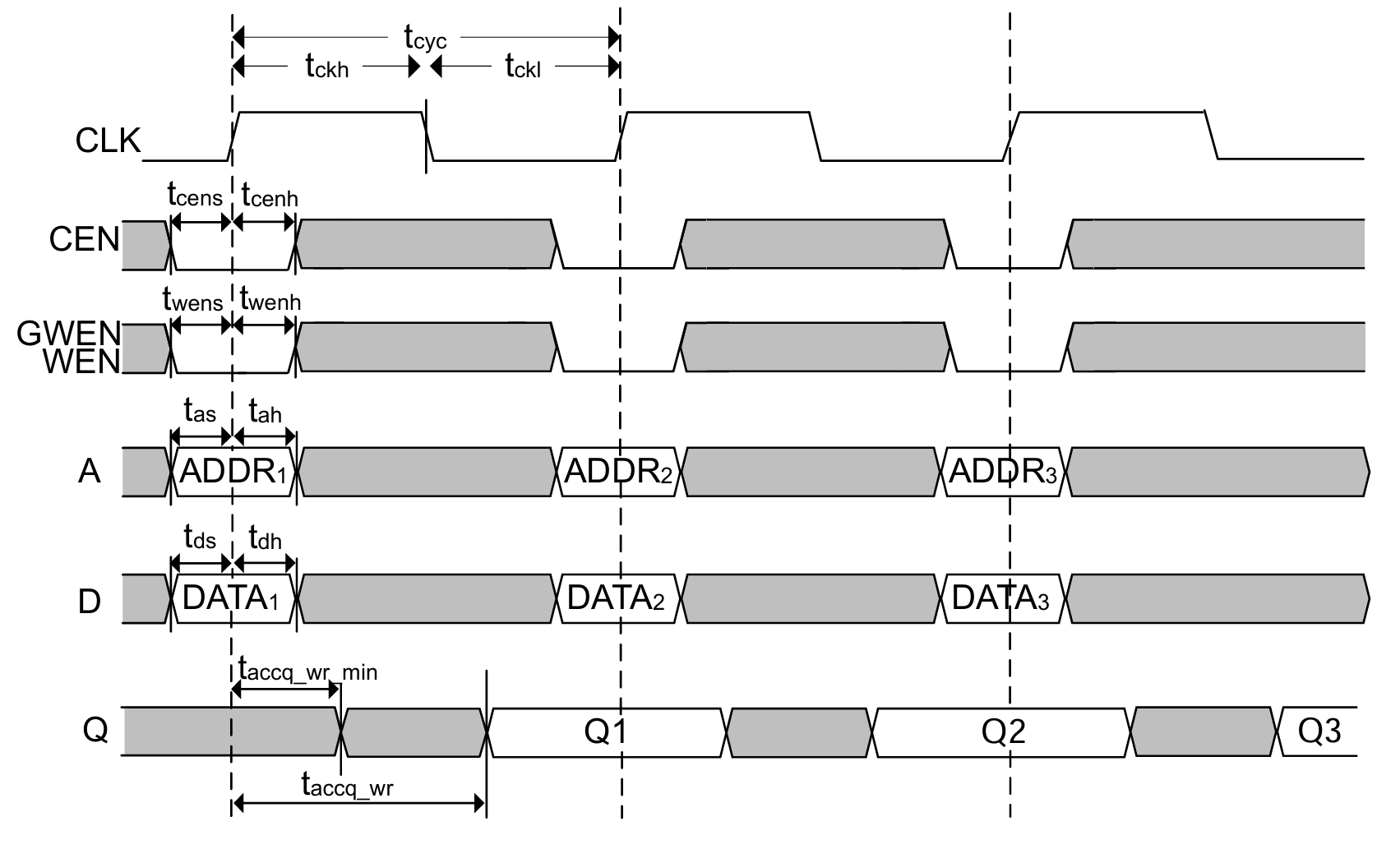

3. 时序